# **UHF FM/AM Transmitter**

The MC13175 and MC13176 are one chip FM/AM transmitter subsystems designed for AM/FM communication systems. They include a Colpitts crystal reference oscillator, UHF oscillator, ÷ 8 (MC13175) or ÷ 32 (MC13176) prescaler and phase detector forming a versatile PLL system. Targeted applications are in the 260 to 470 MHz band and 902 to 928 MHz band covered by FCC Title 47; Part 15. Other applications include local oscillator sources in UHF and 900 MHz receivers, UHF and 900 MHz video transmitters, RF Local Area Networks (LANs), and high frequency clock drivers. The MC13175/76 offer the following features:

- UHF Current Controlled Oscillator

- Uses Easily Available 3rd Overtone or Fundamental Crystals for Reference

- Fewer External Parts Required

- Low Operating Supply Voltage (1.8 to 5.0 Vdc)

- Low Supply Drain Currents

- Power Output Adjustable (Up to +10 dBm)

- Differential Output for Loop Antenna or Balun Transformer Networks

- Power Down Feature

- ASK Modulated by Switching Output On and Off

- (MC13175)  $f_0 = 8 \times f_{ref}$ ; (MC13176)  $f_0 = 32 \times f_{ref}$

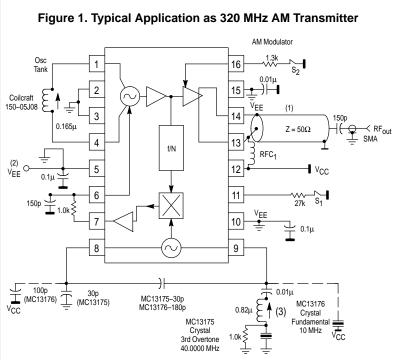

**NOTES:** 1. 50  $\Omega$  coaxial balun, 1/10 wavelength at 320 MHz equals 1.5 inches.

- Pins 5, 10 & 15 are ground and connected to V<sub>EE</sub> which is the component/DC ground plane side of PCB. These pins must be decoupled to V<sub>CC</sub>; decoupling capacitors should be placed as close as possible to the pins.

- 3. The crystal oscillator circuit may be adjusted for frequency with the variable inductor (MC13175); recommended source is Coilcraft "slot seven" 7mm tuneable inductor, Part #7M3–821. 1.0k resistor. Shunting the crystal prevents it from oscillating in the fundamental mode.

## MC13175 MC13176

# UHF FM/AM TRANSMITTER

SEMICONDUCTOR TECHNICAL DATA

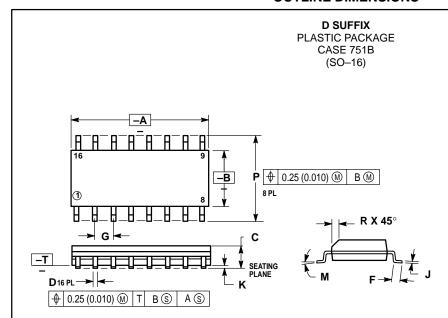

**D SUFFIX**PLASTIC PACKAGE

CASE 751B

(SO–16)

### PIN CONNECTIONS 16 I<sub>mod</sub> Osc 1 15 Ou. Gnd NC 2 14 Out 2 NC 3 Osc 4 4 13 Out 1 VEE 5 12 V<sub>CC</sub> 11 Enable ICont 6 10 Reg. PD<sub>out</sub> | Gnd 9 Xtalb Xtale 8

## ORDERING INFORMATION

| Device   | Operating<br>Temperature Range                      | Package |

|----------|-----------------------------------------------------|---------|

| MC13175D | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | SO-16   |

| MC13176D | 1A = -40 10 +65 C                                   | SO-16   |

**MAXIMUM RATINGS** ( $T_A = 25^{\circ}C$ , unless otherwise noted.)

| Rating                         | Symbol           | Value        | Unit |

|--------------------------------|------------------|--------------|------|

| Power Supply Voltage           | Vcc              | 7.0 (max)    | Vdc  |

| Operating Supply Voltage Range | Vcc              | 1.8 to 5.0   | Vdc  |

| Junction Temperature           | TJ               | +150         | °C   |

| Operating Ambient Temperature  | TA               | - 40 to + 85 | °C   |

| Storage Temperature            | T <sub>stg</sub> | - 65 to +150 | °C   |

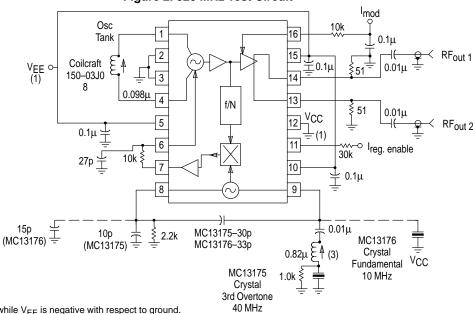

**ELECTRICAL CHARACTERISTICS** (Figure 2;  $V_{EE} = -3.0 \text{ Vdc}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.)\*

| Observatorialia                                                                                                                                                                                             | Di-                | 0                                     | 84:        | T             |        | 1111 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------|------------|---------------|--------|------|

| Characteristic                                                                                                                                                                                              | Pin                | Symbol                                | Min        | Тур           | Max    | Unit |

| Supply Current (Power down: I <sub>11</sub> & I <sub>16</sub> = 0)                                                                                                                                          | _                  | I <sub>EE1</sub>                      | - 0.5      | _             | _      | μΑ   |

| Supply Current (Enable [Pin 11] to V <sub>CC</sub> thru 30 k, I <sub>16</sub> = 0)                                                                                                                          | _                  | I <sub>EE2</sub>                      | -18        | -14           | -      | mA   |

| Total Supply Current (Transmit Mode)<br>(I <sub>mod</sub> = 2.0 mA; f <sub>0</sub> = 320 MHz)                                                                                                               | -                  | I <sub>EE3</sub>                      | - 39       | - 34          | -      | mA   |

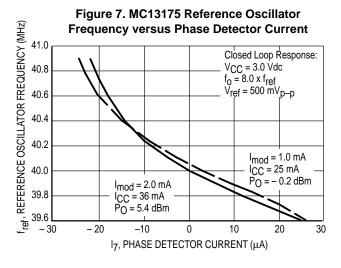

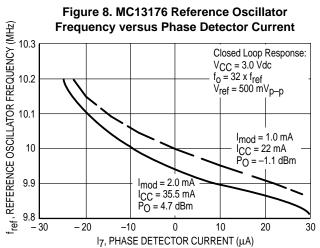

| Differential Output Power ( $f_0 = 320 \text{ MHz}$ ; $V_{ref}$ [Pin 9]<br>= 500 mV <sub>p-p</sub> ; $f_0 = N \times f_{ref}$ )<br>$I_{mod} = 2.0 \text{ mA}$ (see Figure 7, 8)<br>$I_{mod} = 0 \text{ mA}$ | 13 & 14            | Pout                                  | 2.0        | + 4.7<br>- 45 | _<br>_ | dBm  |

| Hold–in Range ( $\pm \Delta f_{ref} \times N$ )<br>MC13175 (see Figure 7)<br>MC13176 (see Figure 8)                                                                                                         | 13 & 14            | ± Δf H                                | 3.5<br>4.0 | 6.5<br>8.0    | _<br>_ | MHz  |

| Phase Detector Output Error Current<br>MC13175<br>MC13176                                                                                                                                                   | 7                  | l <sub>error</sub>                    | 20<br>22   | 25<br>27      | -<br>- | μА   |

| Oscillator Enable Time (see Figure 22b)                                                                                                                                                                     | 11 & 8             | <sup>t</sup> enable                   | -          | 4.0           | -      | ms   |

| Amplitude Modulation Bandwidth (see Figure 24)                                                                                                                                                              | 16                 | BW <sub>AM</sub>                      | -          | 25            | -      | MHz  |

| Spurious Outputs (I <sub>mod</sub> = 2.0 mA)<br>Spurious Outputs (I <sub>mod</sub> = 0 mA)                                                                                                                  | 13 & 14<br>13 & 14 | P <sub>son</sub><br>P <sub>soff</sub> | -<br>-     | - 50<br>- 50  | -<br>- | dBc  |

| Maximum Divider Input Frequency<br>Maximum Output Frequency                                                                                                                                                 | -<br>13 & 14       | fdiv<br>f <sub>o</sub>                | _<br>_     | 950<br>950    | -<br>- | MHz  |

$<sup>^{\</sup>star}$  For testing purposes, VCC is ground (see Figure 2).

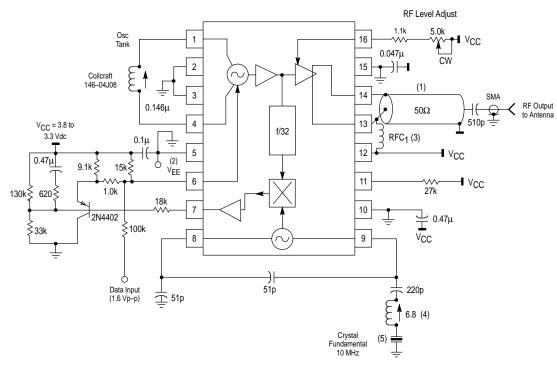

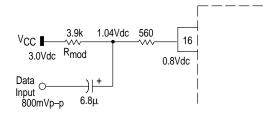

Figure 2. 320 MHz Test Circuit

**NOTES:** 1.  $V_{CC}$  is ground; while  $V_{EE}$  is negative with respect to ground. 40 MHz 2. Pins 5, 10 and 15 are brought to the circuit side of the PCB via plated through holes.

They are connected together with a trace on the PCB and each Pin is decoupled to V<sub>CC</sub> (ground).

<sup>3.</sup> Recommended source is Coilcraft "slot seven" inductor, part number 7M3-821.

## PIN FUNCTION DESCRIPTIONS

| Pin   | Symbol            | Internal Equivalent<br>Circuit                  | Description/External<br>Circuit Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 & 4 | Osc 1,<br>Osc 4   | 10k \$ 10k 10 0sc 1 \$ 0sc 4                    | CCO Inputs  The oscillator is a current controlled type. An external oscillator coil is connected to Pins 1 and 4 which forms a parallel resonance LC tank circuit with the internal capacitance of the IC and with parasitic capacitance of the PC board. Three base—emitter capacitances in series configuration form the capacitance for the parallel tank. These are the base—emitters at Pins 1 and 4 and the base—emitter of the differential amplifier. The equivalent series capacitance in the differential amplifier is varied by the modulating current from the frequency control circuit (see Pin 6, internal circuit). A more thorough discussion is found in the Applications Information section.                                                                                                          |

| 5     | VEE               | VEE 5 Subcon                                    | Supply Ground (VEE) In the PCB layout, the ground pins (also applies to Pins 10 and 15) should be connected directly to chassis ground. Decoupling capacitors to VCC should be placed directly at the ground returns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

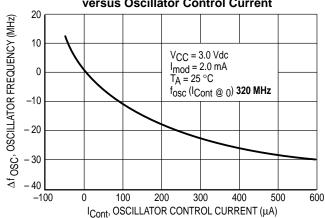

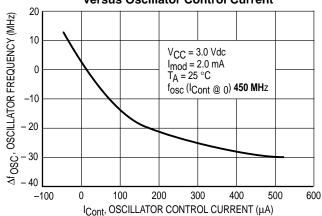

| 6     | lCont             | VCC Reg                                         | Frequency Control For $V_{CC}=3.0$ Vdc, the voltage at Pin 6 is approximately 1.55 Vdc. The oscillator is current controlled by the error current from the phase detector. This current is amplified to drive the current source in the oscillator section which controls the frequency of the oscillator. Figures 9 and 10 show the $\Delta f_{OSC}$ versus $I_{Cont}$ , Figure 5 shows the $\Delta f_{OSC}$ versus $I_{Cont}$ at $-40^{\circ}$ C, $+25^{\circ}$ C and $+85^{\circ}$ C for 320 MHz. The CCO may be FM modulated as shown in Figure 17, MC13176 320 MHz FM Transmitter. A detailed discussion is found in the Applications Information section.                                                                                                                                                            |

| 7     | PD <sub>out</sub> | VCC<br>4.0k<br>4.0k<br>PD <sub>out</sub><br>0 7 | Phase Detector Output The phase detector provides $\pm$ 30 $\mu$ A to keep the CCO locked at the desired carrier frequency. The output impedance of the phase detector is approximately 53 k $\Omega$ . Under closed loop conditions there is a DC voltage which is dependent upon the free running oscillator and the reference oscillator frequencies. The circuitry between Pins 7 and 6 should be selected for adequate loop filtering necessary to stabilize and filter the loop response. Low pass filtering between Pin 7 and 6 is needed so that the corner frequency is well below the sum of the divider and the reference oscillator frequencies, but high enough to allow for fast response to keep the loop locked. Refer to the Applications Information section regarding loop filtering and FM modulation. |

## PIN FUNCTION DESCRIPTIONS

| Pin     | Symbol             | Internal Equivalent<br>Circuit     | Description/External<br>Circuit Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | Xtale<br>Xtalb     | yCCC<br>9 Xtalb<br>8 Xtale<br>4.0k | Crystal Oscillator Inputs  The internal reference oscillator is configured as a common emitter Colpitts. It may be operated with either a fundamental or overtone crystal depending on the carrier frequency and the internal prescaler. Crystal oscillator circuits and specifications of crystals are discussed in detail in the applications section.  With V <sub>CC</sub> = 3.0 Vdc, the voltage at Pin 8 is approximately 1.8 Vdc and at Pin 9 is approximately 2.3 Vdc. 500 to 1000 mVp–p should be present at Pin 9. The Colpitts is biased at 200 μA; additional drive may be acquired by increasing the bias to approximately 500 μA. Use 6.2 k from Pin 8 to ground.                                                                                                                          |

| 10      | Reg. Gnd           | VCC Reg                            | Regulator Ground  An additional ground pin is provided to enhance the stability of the system. Decoupling to the V <sub>CC</sub> (RF ground) is essential; it should be done at the ground return for Pin 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11      | Enable             | 5.0p  Subcon  Reg. Gnd             | <b>Device Enable</b> The potential at Pin 11 is approximately 1.25 Vdc. When Pin 11 is open, the transmitter is disabled in a power down mode and draws less than 1.0 μA $I_{CC}$ if the MOD at Pin 16 is also open (i.e., it has no current driving it). To enable the transmitter a current source of 10 μA to 90 μA is provided. Figures 3 and 4 show the relationship between $I_{CC}$ , $V_{CC}$ and $I_{reg}$ . enable. Note that $I_{CC}$ is flat at approximately 10 mA for $I_{reg}$ . enable = 5.0 to 100 μA ( $I_{mod}$ = 0).                                                                                                                                                                                                                                                                 |

| 12      | Vcc                | Vcc<br>T<br>O<br>12<br>Vcc         | Supply Voltage (VCC) The operating supply voltage range is from 1.8 Vdc to 5.0 Vdc. In the PCB layout, the VCC trace must be kept as wide as possible to minimize inductive reactances along the trace; it is best to have it completely fill around the surface mount components and traces on the circuit side of the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13 & 14 | Out 1 and<br>Out 2 | V <sub>CC</sub>                    | Differential Output The output is configured differentially to easily drive a loop antenna. By using a transformer or balun, as shown in the application schematic, the device may then drive an unbalanced low impedance load. Figure 6 shows how much the Output Power and Free–Running Oscillator Frequency change with temperature at 3.0 Vdc; I <sub>mod</sub> = 2.0 mA.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15      | Out_Gnd            | 13 14 16 I <sub>mod</sub>          | Output Ground This additional ground pin provides direct access for the output ground to the circuit board V <sub>EE</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

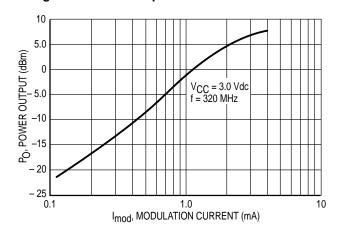

| 16      | Imod               | 15 Out_Gnd                         | AM Modulation/Power Output Level The DC voltage at this pin is 0.8 Vdc with the current source active. An external resistor is chosen to provide a source current of 1.0 to 3.0 mA, depending on the desired output power level at a given V <sub>CC</sub> . Figure 23 shows the relationship of Power Output to Modulation Current, I <sub>mod</sub> . At V <sub>CC</sub> = 3.0 Vdc, 3.5 dBm power output can be acquired with about 35 mA I <sub>CC</sub> . For FM modulation, Pin 16 is used to set the desired output power level as described above.  For AM modulation, the modulation signal must ride on a positive DC bias offset which sets a static (modulation off) modulation current. External circuitry for various schemes is further discussed in the Applications Information section. |

Figure 3. Supply Current versus Supply Voltage 10 I<sub>CC</sub>, SUPPLY CURRENT (mA) lreg. enable = 90 μA 8.0  $I_{mod} = 0$ 6.0 4.0 2.0 0 0 1.0 2.0 3.0 4.0 5.0 VCC, SUPPLY VOLTAGE (Vdc)

Figure 4. Supply Current versus Regulator Enable Current

100

VCC = 3.0 Vdc

Imod = 0

1.0

1.0

Ireg. enable, REGULATOR ENABLE CURRENT (µA)

Figure 6. Change in Oscillator Frequency and **Output Power versus Ambient Temperature** 4.0 5.5 OSCILLATOR FREQUENCY (MHz)  $\Delta f_{\hbox{\scriptsize OSC}}$ Po 3.0 OUTPUT POWER (dBm) 2.0 1.0 0 -1.0 $V_{CC} = 3.0 \text{ Vdc}$ -2.0Imod = 2.0 mA f = 320 MHz (I<sub>Cont</sub> = 0; T<sub>A</sub> = 25°C) Free–Running Oscillator 3.5 🖒 OSC, 3.0 ₹ 3.0 0 - 50 100 TA, AMBIENT TEMPERATURE (°C)

Figure 9. Change in Oscillator Frequency versus Oscillator Control Current

Figure 10. Change in Oscillator Frequency versus Oscillator Control Current

#### **APPLICATIONS INFORMATION**

#### **Evaluation PC Board**

The evaluation PCB, shown in Figures 26 and 27, is very versatile and is intended to be used across the entire useful frequency range of this device. The center section of the board provides an area for attaching all SMT components to the circuit side and radial leaded components to the component ground side of the PCB (see Figures 28 and 29). Additionally, the peripheral area surrounding the RF core provides pads to add supporting and interface circuitry as a particular application dictates. This evaluation board will be discussed and referenced in this section.

#### **Current Controlled Oscillator (Pins 1 to 4)**

It is critical to keep the interconnect leads from the CCO (Pins 1 and 4) to the external inductor symmetrical and equal in length. With a minimum inductor, the maximum free running frequency is greater than 1.0 GHz. Since this inductor will be small, it may be either a microstrip inductor, an air wound inductor or a tuneable RF coil. An air wound inductor may be tuned by spreading the windings, whereas tuneable RF coils are tuned by adjusting the position of an aluminum core in a threaded coilform. As the aluminum core coupling to the windings is increased, the inductance is decreased. The temperature coefficient using an aluminum core is better than a ferrite core. The UniCoil™ inductors made by Coilcraft may be obtained with aluminum cores (Part No. 51–129–169).

#### Ground (Pins 5, 10 and 15)

**Ground Returns:** It is best to take the grounds to a backside ground plane via plated through holes or eyelets at the pins. The application PCB layout implements this technique. Note that the grounds are located at or less than 100 mils from the devices pins.

**Decoupling:** Decoupling each ground pin to  $V_{CC}$  isolates each section of the device by reducing interaction between sections and by localizing circulating currents.

#### Loop Characteristics (Pins 6 and 7)

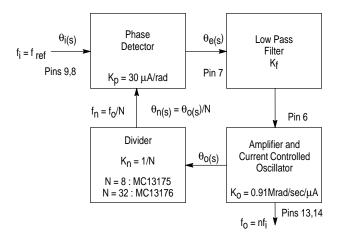

Figure 11 is the component block diagram of the MC1317XD PLL system where the loop characteristics are described by the gain constants. Access to individual components of this PLL system is limited, inasmuch as the loop is only pinned out at the phase detector output and the

frequency control input for the CCO. However, this allows for characterization of the gain constants of these loop components. The gain constants  $K_p$ ,  $K_0$  and  $K_n$  are well defined in the MC13175 and MC13176.

#### Phase Detector (Pin 7)

With the loop in lock, the difference frequency output of the phase detector is DC voltage that is a function of the phase difference. The sinusoidal type detector used in this IC has the following transfer characteristic:

$$I_e = A \sin \theta_e$$

The gain factor of the phase detector,  $K_p$  (with the loop in lock) is specified as the ratio of DC output current,  $I_e$  to phase error,  $\theta_e$ :

$K_p = I_e/\theta_e$  (Amps/radians)

$K_D = A \sin \theta_e/\theta_e$

Sin  $\theta_e \sim \theta_e$  for  $\theta_e \leq 0.2$  radians;

thus,  $K_D = A$  (Amps/radians)

Figures 7 and 8 show that the detector DC current is approximately 30  $\mu$ A where the loop loses lock at  $\theta_e = \pm \pi/2$  radians; therefore,  $K_D$  is 30  $\mu$ A/radians.

#### **Current Controlled Oscillator, CCO (Pin 6)**

Figures 9 and 10 show the non-linear change in frequency of the oscillator over an extended range of control current for 320 and 450 MHz applications. Ko ranges from approximately 6.3x10<sup>5</sup> rad/sec/μA or 100 kHz/μA (Figure 9) to 8.8x10<sup>5</sup> rad/sec/μA or 140 kHz/μA (Figure 10) over a relatively linear response of control current (0 to 100  $\mu$ A). The oscillator gain factor depends on the operating range of the control current (i.e., the slope is not constant). Included in the CCO gain factor is the internal amplifier which can sink and source at least 30 µA of input current from the phase detector. The internal circuitry at Pin 6 limits the CCO control current to 50 µA of source capability while its sink capability exceeds 200 µA as shown in Figures 9 and 10. Further information to follow shows how to use the full capabilities of the CCO by addition of an external loop amplifier and filter (see Figure 15). This additional circuitry yields at  $K_0 =$ 0.145 MHz/μA or 9.1x10<sup>5</sup> rad/sec/μA.

Figure 11. Block Diagram of MC1317XD PLL

Where:  $K_p$  = Phase detector gain constant in  $\mu A/rad$ ;  $K_p$  = 30  $\mu A/rad$   $K_f$  = Filter transfer function  $K_n$  = 1/N; N = 8 for the MC13175 and  $K_0$  N = 32 for the MC13176 = CCO gain constant in rad/sec/ $\mu A$

$K_0 = 9.1 \times 10^5 \text{ rad/sec/}\mu\text{A}$

#### **Loop Filtering**

The fundamental loop characteristics, such as capture range, loop bandwidth, lock—up time and transient response are controlled externally by loop filtering.

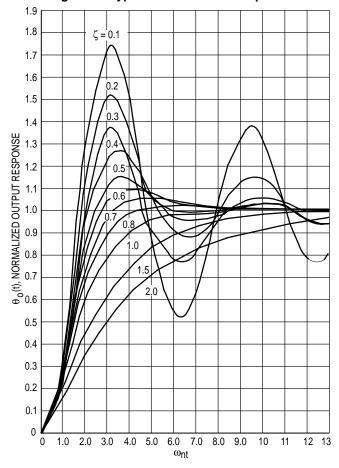

The natural frequency  $(\omega_{\text{N}})$  and damping factor  $(\partial)$  are important in the transient response to a step input of phase or frequency. For a given  $\partial$  and lock time,  $\omega_{\text{N}}$  can be determined from the plot shown in Figure 12.

Figure 12. Type 2 Second Order Response

For  $\partial = 0.707$  and lock time = 1.0 ms; then  $\omega_n = 5.0/t = 5.0$  krad/sec.

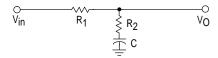

The loop filter may take the form of a simple low pass filter or a lag–lead filter which creates an additional pole at origin in the loop transfer function. This additional pole along with that of the CCO provides two pure integrators (1/s²). In the lag–lead low pass network shown in Figure 13, the values of the low pass filtering parameters  $R_1$ ,  $R_2$  and C determine the loop constants  $\omega_n$  and  $\partial$ . The equations  $t_1 = R_1C$  and  $t_2 = R_2C$  are related in the loop filter transfer functions  $F(s) = 1 + t_2s/1 + (t_1 + t_2)s$ .

Figure 13. Lag-Lead Low Pass Filter

The closed loop transfer function takes the form of a 2nd order low pass filter given by,

$$H(s) = K_V F(s)/s + K_V F(s)$$

From control theory, if the loop filter characteristic has F(0) = 1, the DC gain of the closed loop,  $K_V$  is defined as,

$$K_V = K_D K_O K_D$$

and the transfer function has a natural frequency,

$$\omega_{\rm n} = (K_{\rm V}/t_1 + t_2)^{1/2}$$

and a damping factor,

$$\partial = (\omega_0/2) (t_2 + 1/K_V)$$

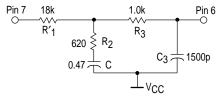

Rewriting the above equations and solving for the MC13176 with  $\partial=0.707$  and  $\omega_{\text{N}}=5.0$  k rad/sec:

$$\begin{split} &K_V = K_p K_0 K_n = (30) \; (0.91 \, \times \, 10^6) \; (1/32) = 0.853 \, \times \, 10^6 \\ &t_1 + t_2 = K_V / \omega_n 2 = 0.853 \, \times \, 10^6 / (25 \, \times \, 106) = 34.1 \; \text{ms} \\ &t_2 = 2\partial / \omega_n = (2) \; (0.707) / (5 \, \times \, 10^3) = 0.283 \; \text{ms} \\ &t_1 = (K_V / \omega_n 2) - t_2 = (34.1 - 0.283) = 33.8 \; \text{ms} \end{split}$$

For C =  $0.47 \mu$ ;

then, R<sub>1</sub> =  $t_1/C$  = 33.8  $\times$  10<sup>-3</sup>/0.47  $\times$  10<sup>-6</sup> = 72 k dthus, R<sub>2</sub> =  $t_2/C$  = 0.283  $\times$  10<sup>-3</sup>/0.47  $\times$  10<sup>-6</sup> = 0.60 k In the above example, the following standard value components are used,

$C = 0.47 \mu$ ;  $R_2 = 620$  and  $R'_1 = 72 k - 53 k ~ 18 k$

$(R'_1)$  is defined as  $R_1 - 53$  k, the output impedance of the phase detector.)

Since the output of the phase detector is high impedance ( $\sim$ 50 k) and serves as a current source, and the input to the frequency control, Pin 6 is low impedance (impedance of the two diode to ground is approximately 500  $\Omega$ ), it is imperative that the second order low pass filter design above be modified. In order to minimize loading of the R<sub>2</sub>C shunt network, a higher impedance must be established to Pin 6. A simple solution is achieved by adding a low pass network between the passive second order network and the input to Pin 6. This helps to minimize the loading effects on the second order low pass while further suppressing the sideband spurs of the crystal oscillator. A low pass filter with R<sub>3</sub> = 1.0 k and C<sub>2</sub> = 1500 p has a corner frequency (f<sub>C</sub>) of 106 kHz; the reference sideband spurs are down greater than – 60 dBc.

Figure 14. Modified Low Pass Loop Filter

#### Hold-In Range

The hold–in range, also called the lock range, tracking range and synchronization range, is the ability of the CCO frequency,  $f_0$  to track the input reference signal,  $f_{\text{ref}} \bullet N$  as it gradually shifted away from the free running frequency,  $f_f$ . Assuming that the CCO is capable of sufficient frequency deviation and that the internal loop amplifier and filter are not overdriven, the CCO will track until the phase error,  $\theta_{\text{e}}$  approaches  $\pm \pi/2$  radians. Figures 5 through 8 are a direct

measurement of the hold–in range (i.e.  $\Delta f_{ref} \times N = \pm \Delta f_{H} \times 2\pi$ ). Since  $\sin \theta_{e}$  cannot exceed  $\pm 1.0$ , as  $\theta_{e}$  approaches  $\pm \pi/2$  the hold–in range is equal to the DC loop gain,  $K_{V} \times N$ .

$$\pm \Delta \omega_H = \pm K_V \times N$$

where,  $K_V = K_D K_O K_D$ .

In the above example,

$\pm\Delta\omega_{\text{H}} = \pm 27.3 \text{ Mrad/sec}$  $\pm\Delta f_{\text{H}} = \pm 4.35 \text{ MHz}$

#### Extended Hold-in Range

The hold–in range of about 3.4% could cause problems over temperature in cases where the free–running oscillator drifts more than 2 to 3% because of relatively high temperature coefficients of the ferrite tuned CCO inductor. This problem might worsen for lower frequency applications where the external tuning coil is large compared to internal capacitance at Pins 1 and 4. To improve hold–in range performance, it is apparent that the gain factors involved must be carefully considered.

$K_{\text{n}} = \text{is either } 1/8 \text{ in the MC13175 or } 1/32 \text{ in the MC13176}.$

$K_D$  = is fixed internally and cannot be altered.

$\dot{K_0}$  = Figures 9 and 10 suggest that there is capability of greater control range with more current swing. However, this swing must be symmetrical about the center of the dynamic response. The suggested zero current operating point for  $\pm 100~\mu A$  swing of the CCO is at about + 70  $\mu A$  offset point.

Ka = External loop amplification will be necessary since the phase detector only supplies  $\pm 30 \mu A$ .

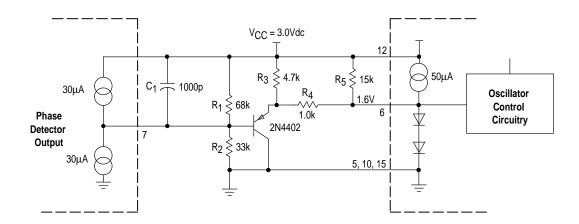

In the design example in Figure 15, an external resistor (R<sub>5</sub>) of 15 k to V<sub>CC</sub> (3.0 Vdc) provides approximately 100  $\mu$ A of current boost to supplement the existing 50  $\mu$ A internal source current. R<sub>4</sub> (1.0 k) is selected for approximately 0.1 Vdc across it with 100  $\mu$ A. R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub> are selected to set the potential at Pin 7 and the base of 2N4402 at approximately 0.9 Vdc and the emitter at 1.55 Vdc when error current to Pin 6 is approximately zero  $\mu$ A. C<sub>1</sub> is chosen to reduce the level of the crystal sidebands.

Figure 15. External Loop Amplifier

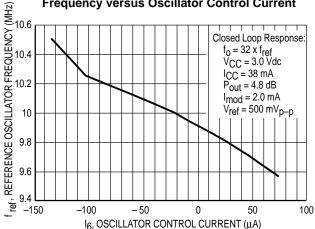

Figure 16 shows the improved hold–in range of the loop. The  $\Delta f_{ref}$  is moved 950 kHz with over 200  $\mu A$  swing of control current for an improved hold–in range of  $\pm 15.2$  MHz or  $\pm$  95.46 Mrad/sec.

Figure 16. MC13176 Reference Oscillator Frequency versus Oscillator Control Current

#### Lock-in Range/Capture Range

If a signal is applied to the loop not equal to free running frequency,  $f_f$ , then the loop will capture or lock—in the signal by making  $f_S=f_O$  (i.e. if the initial frequency difference is not too great). The lock—in range can be expressed as  $\Delta\omega_L\sim\pm~2\partial\omega_D$

#### **FM Modulation**

Noise external to the loop (phase detector input) is minimized by narrowing the bandwidth. This noise is minimal in a PLL system since the reference frequency is usually derived from a crystal oscillator. FM can be achieved by applying a modulation current superimposed on the control current of the CCO. The loop bandwidth must be narrow enough to prevent the loop from responding to the modulation frequency components, thus, allowing the CCO to deviate in frequency. The loop bandwidth is related to the natural frequency  $\omega_{\text{n}}$ . In the lag–lead design example where the natural frequency,  $\omega_{\text{N}}$  = 5.0 krad/sec and a damping factor,  $\partial = 0.707$ , the loop bandwidth = 1.64 kHz. Characterization data of the closed loop responses for both the MC13175 and MC13176 at 320 MHz (Figures 7 and 8, respectively) show satisfactory performance using only a simple low-pass loop filter network. The loop filter response is strongly influenced by the high output impedance of the push-pull current output of the phase detector.

$f_{C} = 0.159/RC;$

For  $R = 1.0 \text{ k} + R_7 (R_7 = 53 \text{ k})$  and C = 390 pF

$f_C = 7.55 \text{ kHz or } \omega_C = 47 \text{ krad/sec}$

The application example in Figure 17a of a 320 MHz FM transmitter demonstrates the FM capabilities of the IC. A high value series resistor (100 k) to Pin 6 sets up the current source to drive the modulation section of the chip. Its value is dependent on the peak to peak level of the encoding data and the maximum desired frequency deviation. The data input is AC coupled with a large coupling capacitor which is selected for the modulating frequency. The component placements on the circuit side and ground side of the PC board are shown in Figures 28 and 29, respectively. Figure 18a illustrates the input data of a 10 kHz modulating signal at 1.6 Vp–p. Figures 18b and 18c depict the deviation and resulting modulation spectrum showing the carrier null at – 40 dBc. Figure 18d shows the unmodulated carrier power output at 3.5 dBm for VCC = 3.0 Vdc.

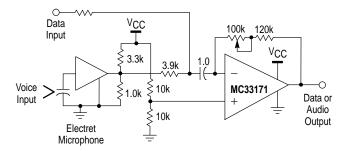

For voice applications using a dynamic or an electret microphone, an op amp is used to amplify the microphone's low level output. The microphone amplifier circuit is shown in Figure 19. Figure 17b shows an application example for NBFM audio or direct FSK in which the reference crystal oscillator is modulated.

Figure 19. Microphone Amplifier

#### **Local Oscillator Application**

To reduce internal loop noise, a relatively wide loop bandwidth is needed so that the loop tracks out or cancels the noise. This is emphasized to reduce inherent CCO and divider noise or noise produced by mechanical shock and environmental vibrations. In a local oscillator application the CCO and divider noise should be reduced by proper selection of the natural frequency of the loop. Additional low pass filtering of the output will likely be necessary to reduce the crystal sideband spurs to a minimal level.

Figure 17a. 320 MHz MC13176D FM Transmitter

NOTES: 1.50  $\Omega$  coaxial balun, 2 inches long.

- Pins 5, 10 and 15 are grounds and connnected to V<sub>EE</sub> which is the component's side ground plane.These pins must be decoupled to V<sub>CC</sub>; decoupling capacitors should be placed as close as possible to the pins.

- 3. RFC<sub>1</sub> is 180 nH Coilcraft surface mount inductor or 190 nH Coilcraft 146–05J08.

- 4. Recommended source is a Coilcraft "slot seven" 7.0 mm tuneable inductor, part #7M3-682.

- 5. The crystal is a parallel resonant, fundamental mode calibrated with 32 pF load capacitance.

RF Level Adjust 1.0k Osc 16  $0.047\mu$ CW 15 Coilcraft 146–04J08 (1) 14 RF Output  $0.146 \mu$ UT-034 13 f/32 Vcc RFC<sub>1</sub> (3)  $0.1 \mu$ 12 5 ■ V<sub>CC</sub> (3.6 Vdc – Lithium Battery) 4700p (2) 15k ¶ V<sub>CC</sub> 6 11 27k 1.0k 130k ≶ 6.2k 10 <sup>1</sup>2N4402 0.47μ T VCC 33k 8 9 (4) 10p External 10μ Loop Amp RFC<sub>3</sub> 100p 180p 0.01μ (6) Crystal Fundamental 10MHz (5) MMBV432L Audio or Data Input

Figure 17b. 320 MHz NBFM Transmitter

NOTES: 1.50  $\Omega$  coaxial balun, 2 inches long.

- Pins 5, 10 and 15 are grounds and connected to V<sub>EE</sub> which is the component's side ground plane. These

pins must be decoupled to V<sub>CC</sub>; decoupling capacitors should be placed as close as possible to the pins.

- 3. RFC<sub>1</sub> is 180 nH Coilcraft surface mount inductor.

- 4. RFC $_2$  and RFC $_3$  are high impedance crystal frequency of 10 MHz; 8.2  $\mu$ H molded inductor gives XL > 1000  $\Omega$ .

- 5. A single varactor like the MV2105 may be used whereby RFC<sub>2</sub> is not needed.

- 6. The crystal is a parallel resonant, fundamental mode calibrated with 32 pF load capacitance.

Graphics not available electronically.

For complete document,

order from the Literature Distribution

Center.

Figure 18c. Modulation Spectrum

Figure 18d. Unmodulated Carrier

#### Reference Crystal Oscillator (Pins 8 and 9)

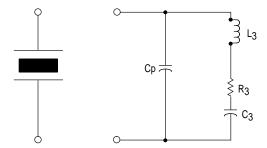

Selection of Proper Crystal: A crystal can operate in a number of mechanical modes. The lowest resonant frequency mode is its fundamental while higher order modes are called overtones. At each mechanical resonance, a crystal behaves like a RLC series—tuned circuit having a large inductor and a high Q. The inductor  $L_{\rm S}$  is series resonance with a dynamic capacitor,  $C_{\rm S}$  determined by the elasticity of the crystal lattice and a series resistance  $R_{\rm S}$ , which accounts for the power dissipated in heating the crystal. This series RLC circuit is in parallel with a static capacitance,  $C_{\rm P}$  which is created by the crystal block and by the metal plates and leads that make contact with it.

Figure 20 is the equivalent circuit for a crystal in a single resonant mode. It is assumed that other modes of resonance are so far off frequency that their effects are negligible.

Series resonant frequency,  $f_S$  is given by;

$$f_S = 1/2\pi (L_S C_S)^{1/2}$$

and parallel resonant frequency, fp is given by;

$$f_p = f_s(1 + C_s/C_p)^{1/2}$$

Figure 20. Crystal Equivalent Circuit

the frequency separation at resonance is given by;

$$\Delta f = f_D - f_S = f_S [1 - (1 + C_S/C_D)^{1/2}]$$

Usually  $f_p$  is less than 1% higher than  $f_s$ , and a crystal exhibits an extremely wide variation of the reactance with frequency between  $f_p$  and  $f_s$ . A crystal oscillator circuit is very stable with frequency. This high rate of change of impedance with frequency stabilizes the oscillator, because any significant change in oscillator frequency will cause a large phase shift in the feedback loop keeping the oscillator on frequency.

Manufacturers specify crystal for either series or parallel resonant operation. The frequency for the parallel mode is calibrated with a specified shunt capacitance called a "load capacitance." The most common value is 30 to 32 pF. If the load capacitance is placed in series with the crystal, the equivalent circuit will be series resonance at the specified parallel—resonant frequency. Frequencies up to 20 MHz use parallel resonant crystal operating in the fundamental mode, while above 20 MHz to about 60 MHz, a series resonant crystal specified and calibrated for operation in the overtone mode is used.

#### **Application Examples**

Two types of crystal oscillator circuits are used in the applications circuits: 1) fundamental mode common emitter Colpitts (Figures 1, 17a, 17b, and 21), and 2) third overtone impedance inversion Colpitts (also Figures 1 and 21).

The fundamental mode common emitter Colpitts uses a parallel resonant crystal calibrated with a 32 pf load capacitance. The capacitance values are chosen to provide excellent frequency stability and output power of > 500 mVp-p at Pin 9. In Figures 1 and 21, the fundamental mode reference oscillator is fixed tuned relying on the repeatability of the crystal and passive network to maintain the frequency, while in the circuit shown in Figure 17, the oscillator frequency can be adjusted with the variable inductor for the precise operating frequency.

The third overtone impedance inversion Colpitts uses a series resonance crystal with a 25 ppm tolerance. In the application examples (Figures 1 and 21), the reference oscillator operates with the third overtone crystal at 40.0000 MHz. Thus, the MC13175 is operated at 320 MHz (f<sub>0</sub>/8 = crystal; 320/8 = 40.0000 MHz. The resistor across the crystal ensures that the crystal will operate in the series resonant mode. A tuneable inductor is used to adjust the oscillation frequency; it forms a parallel resonant circuit with the series and parallel combination of the external capacitors forming the divider and feedback network and the base–emitter capacitance of the device. If the crystal is shorted, the reference oscillator should free–run at the frequency dictated by the parallel resonant LC network.

The reference oscillator can be operated as high as 60 MHz with a third overtone crystal. Therefore, it is possible to use the MC13175 up to at least 480 MHz and the MC13176 up to 950 MHz (based on the maximum capability of the divider network).

#### Enable (Pin 11)

The enabling resistor at Pin 11 is calculated by: Reg. enable =  $VCC - 1.0 \text{ Vdc/I}_{reg.}$  enable

From Figure 4, I<sub>reg. enable</sub> is chosen to be 75  $\mu$ A. So, for a V<sub>CC</sub> = 3.0 Vdc R<sub>reg. enable</sub> = 26.6 k $\Omega$ , a standard value 27 k $\Omega$  resistor is adequate.

#### **Layout Considerations**

**Supply (Pin 12):** In the PCB layout, the  $V_{CC}$  trace must be kept as wide as possible to minimize inductive reactance along the trace; it is best that  $V_{CC}$  (RF ground) completely fills around the surface mounted components and interconnect traces on the circuit side of the board. This technique is demonstrated in the evaluation PC board.

#### **Battery/Selection/Lithium Types**

The device may be operated from a 3.0 V lithium battery. Selection of a suitable battery is important. Because one of the major problems for long life battery powered equipment is oxidation of the battery terminals, a battery mounted in a clip-in socket is not advised. The battery leads or contact post should be isolated from the air to eliminate oxide build-up. The battery should have PC board mounting tabs which can be soldered to the PCB. Consideration should be given for the peak current capability of the battery. Lithium batteries have current handling capabilities based on the composition of the lithium compound, construction and the battery size. A 1300 mA/hr rating can be achieved in the cylindrical cell battery. The Rayovac CR2/3A lithium-manganese dioxide battery is a crimp sealed, spiral wound 3.0 Vdc, 1300 mA/hr cylindrical cell with PC board mounting tabs. It is an excellent choice based on capacity and size (1.358" long by 0.665" in diameter).

#### Differential Output (Pins 13, 14)

The availability of micro–coaxial cable and small baluns in surface mount and radial–leaded components allows for simple interface to the output ports. A loop antenna may be directly connected with bias via RFC or 50  $\Omega$  resistors. Antenna configuration will vary depending on the space available and the frequency of operation.

#### AM Modulation (Pin 16)

Amplitude Shift Key: The MC13175 and MC13176 are designed to accommodate Amplitude Shift Keying (ASK). ASK modulation is a form of digital modulation corresponding to AM. The amplitude of the carrier is switched between two or more values in response to the PCM code. For the binary case, the usual choice is On–Off Keying (often abbreviated OOK). The resultant amplitude modulated waveform consists of RF pulses called marks, representing binary 1 and spaces representing binary 0.

R<sub>mod</sub> 3.3k (4) Osc 16 On-Off Keyed Input Tank 0.01u TTL Level 10 kHz 15 2 coilcraft 2 150-05J08 (1)  $0.165 \mu$ **RFOut** Z = 5013 f/N RFC<sub>1</sub> 12 ¶ VCC 11  $V_{\mathsf{EE}}$ 10 0.1μ 8 9 MC13175-30p  $0.01\mu$ 30p MC13176-180p (MC13176) (MC13175)

MC13175

Crystal

3rd Overtone 40.0000 MHz

Figure 21. ASK 320 MHz Application Circuit

- **NOTES:** 1.50  $\Omega$  coaxial balun, 1/10 wavelength line (1.5") provides the best match to a 50  $\Omega$  load.

- 2. Pins 5, 10 and 15 are ground and connnected to  $V_{\mbox{EE}}$  which is the component/DC ground plane side of PCB. These pins must be decoupled to  $V_{\mbox{CC}}$ ; decoupling capacitors should be placed as close as possible to the pins.

- The crystal oscillator circuit may be adjusted for frequency with the variable inductor (MC13175); 1.0 k resistor shunting the crystal prevents it from oscillating in the fundamental mode. Recommended source is Coilcraft "slot seven" 7.0 mm tuneable inductor, part #7N3–821.

- 4. The On–Off keyed signal turns the output of the transmitter off and on with TTL level pulses through R $_{mod}$  at Pin 16. The "On" power and I $_{CC}$  is set by the resistor which sets I $_{mod}$  = VTTL 0.8 / R $_{mod}$ . (see Figure 23).

MC13176 Crystal

**Fundamental**

10 MHz

5. S1 simulates an enable gate pulse from a microprocessor which will enable the transmitter. (see Figure 4 to determine precise value of the enabling resistor based on the potential of the gate pulse and the desired enable.)

Figure 21 shows a typical application in which the output power has been reduced for linearity and current drain. The current draw on the device is 16 mA I<sub>CC</sub> (average) and – 22.5 dBm (average power output) using a 10 kHz modulating rate for the on–off keying. This equates to 20 mA and – 2.3 dBm "On", 13 mA and – 41 dBm "Off". In Figure 22a, the device's modulating waveform and encoded carrier

are displayed. The crystal oscillator enable time is needed to set the acquisition timing. It takes typically 4.0 msec to reach full magnitude of the oscillator waveform (see Figure 22b, Oscillator Waveform, at Pin 8). A square waveform of 3.0 V peak with a period that is greater than the oscillator enable time is applied to the Enable (Pin 11).

Figure 22a. ASK Input Waveform and Modulated Carrier

Graphics not available electronically.

For complete document,

order from the Literature Distribution

Center.

Figure 22b. Oscillator Enable Time, Tenable

Figure 23. Power Output versus Modulation Current

#### **Analog AM**

In analog AM applications, the output amplifier's linearity must be carefully considered. Figure 23 is a plot of Power Output versus Modulation Current at 320 MHz, 3.0 Vdc. In order to achieve a linear encoding of the modulating sinusoidal waveform on the carrier, the modulating signal must amplitude modulate the carrier in the linear portion of its power output response. When using a sinewave modulating signal, the signal rides on a positive DC offset called  $V_{\mbox{mod}}$  which sets a static (modulation off) modulation current,  $I_{\mbox{mod}}$  controls the power output of the IC. As the modulating signal moves around this static bias point the modulating current varies causing power output to vary or to be AM modulated. When the IC is operated at modulation current levels greater than 2.0 mAdc the differential output stage starts to saturate.

In the design example, shown in Figure 24, the operating point is selected as a tradeoff between average power output and quality of the AM.

For V<sub>CC</sub> = 3.0 Vdc; I<sub>CC</sub> = 18.5 mA and I<sub>mod</sub> = 0.5 mAdc and a static DC offset of 1.04 Vdc, the circuit shown in Figure 24 completes the design. Figures 25a, 25b and 25c show the results of -6.9 dBm output power and 100% modulation by the 10 kHz and 1.0 MHz modulating sinewave signals. The amplitude of the input signals is approximately 800 mVp-p.

Where  $R_{mod} = (V_{CC} - 1.04 \text{ Vdc})/0.5 \text{ mA} = 3.92 \text{ k}$ , use a standard value resistor of 3.9 k.

Figure 24. Analog AM Transmitter

Figure 25a. Power Output of Unmodulated Carrier

Graphics not available electronically.

For complete document,

order from the Literature Distribution

Center.

Figure 25b. Input Signal and AM Modulated Carrier for  $f_{mod} = 10 \text{ kHz}$

Figure 25c. Input Signal and AM Modulated

Carrier for f<sub>mod</sub> = 1.0 MHz

Figure 26. Circuit Side View of MC1317XD

Graphics not available electronically.

For complete document,

order from the Literature Distribution

Center.

Figure 27. Ground Side View

Figure 28. Surface Mounted Components Placement (on Circuit Side)

Graphics not available electronically.

For complete document,

order from the Literature Distribution

Center.

Figure 29. Radial Leaded Components Placement (on Ground Side)

#### **OUTLINE DIMENSIONS**

#### NOTES

- DIMENSIONING AND TOLERANCING PER ANSI

YA4 FM 4002

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- 751B-01 IS OBSOLETE, NEW STANDARD 751B-03.

|     | MILLIM   | ETERS | INCHES      |       |  |

|-----|----------|-------|-------------|-------|--|

| DIM | MIN      | MAX   | MIN         | MAX   |  |

| Α   | 9.80     | 10.00 | 0.386       | 0.393 |  |

| В   | 3.80     | 4.00  | 0.150       | 0.157 |  |

| С   | 1.35     | 1.75  | 0.054       | 0.068 |  |

| D   | 0.35     | 0.49  | 0.014       | 0.019 |  |

| F   | 0.40     | 1.25  | 0.016       | 0.049 |  |

| G   | 1.27 BSC |       | 0.050 BSC   |       |  |

| J   | 0.19     | 0.25  | 0.008 0.009 |       |  |

| K   | 0.10     | 0.25  | 0.004       | 0.009 |  |

| М   | 0°       | 7°    | 0°          | 7°    |  |

| Р   | 5.80     | 6.20  | 0.229       | 0.244 |  |

| R   | 0.25     | 0.50  | 0.010       | 0.019 |  |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design-NET.com

$\Diamond$

**JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298